Earnings summaries and quarterly performance for CADENCE DESIGN SYSTEMS.

Executive leadership at CADENCE DESIGN SYSTEMS.

Anirudh Devgan

Chief Executive Officer

Chin-Chi Teng

Senior Vice President, Digital and Signoff Group

John Wall

Chief Financial Officer

Paul Cunningham

Senior Vice President, System Verification Group

Paul Scannell

Senior Vice President, Customer Success Team

Board of directors at CADENCE DESIGN SYSTEMS.

Research analysts who have asked questions during CADENCE DESIGN SYSTEMS earnings calls.

Jason Celino

KeyBanc Capital Markets

8 questions for CDNS

Jay Vleeschhouwer

Griffin Securities, Inc.

8 questions for CDNS

Joshua Tilton

Wolfe Research

8 questions for CDNS

Lee Simpson

Morgan Stanley

8 questions for CDNS

Ruben Roy

Stifel Financial Corp.

8 questions for CDNS

Vivek Arya

Bank of America Corporation

8 questions for CDNS

Gary Mobley

Loop Capital

7 questions for CDNS

Gianmarco Conti

Deutsche Bank AG

7 questions for CDNS

Charles Shi

Needham & Company

6 questions for CDNS

Harlan Sur

JPMorgan Chase & Co.

6 questions for CDNS

Joe Quatrochi

Wells Fargo

5 questions for CDNS

Joe Vruwink

Baird

5 questions for CDNS

Clarke Jeffries

Piper Sandler & Co.

4 questions for CDNS

Jim Schneider

Goldman Sachs

4 questions for CDNS

Nay Soe Naing

Berenberg Capital Markets LLC

3 questions for CDNS

Sitikantha Panigrahi

Mizuho

3 questions for CDNS

Siti Panigrahi

Mizuho Securities

3 questions for CDNS

Andrew DeGasperi

BNP Paribas

2 questions for CDNS

Blair Abernethy

Rosenblatt Securities Inc.

2 questions for CDNS

Joseph Quatrochi

Wells Fargo Securities, LLC

2 questions for CDNS

Joseph Vruwink

Baird

2 questions for CDNS

Kelsey Chia

Citigroup Inc.

2 questions for CDNS

Siddhi Panigrahi

Mizuho

2 questions for CDNS

James Schneider

Goldman Sachs

1 question for CDNS

John Marco Conti

Deutsche Bank

1 question for CDNS

Naso Nain

Berenberg

1 question for CDNS

Yu Shi

Susquehanna International Group, LLP

1 question for CDNS

Recent press releases and 8-K filings for CDNS.

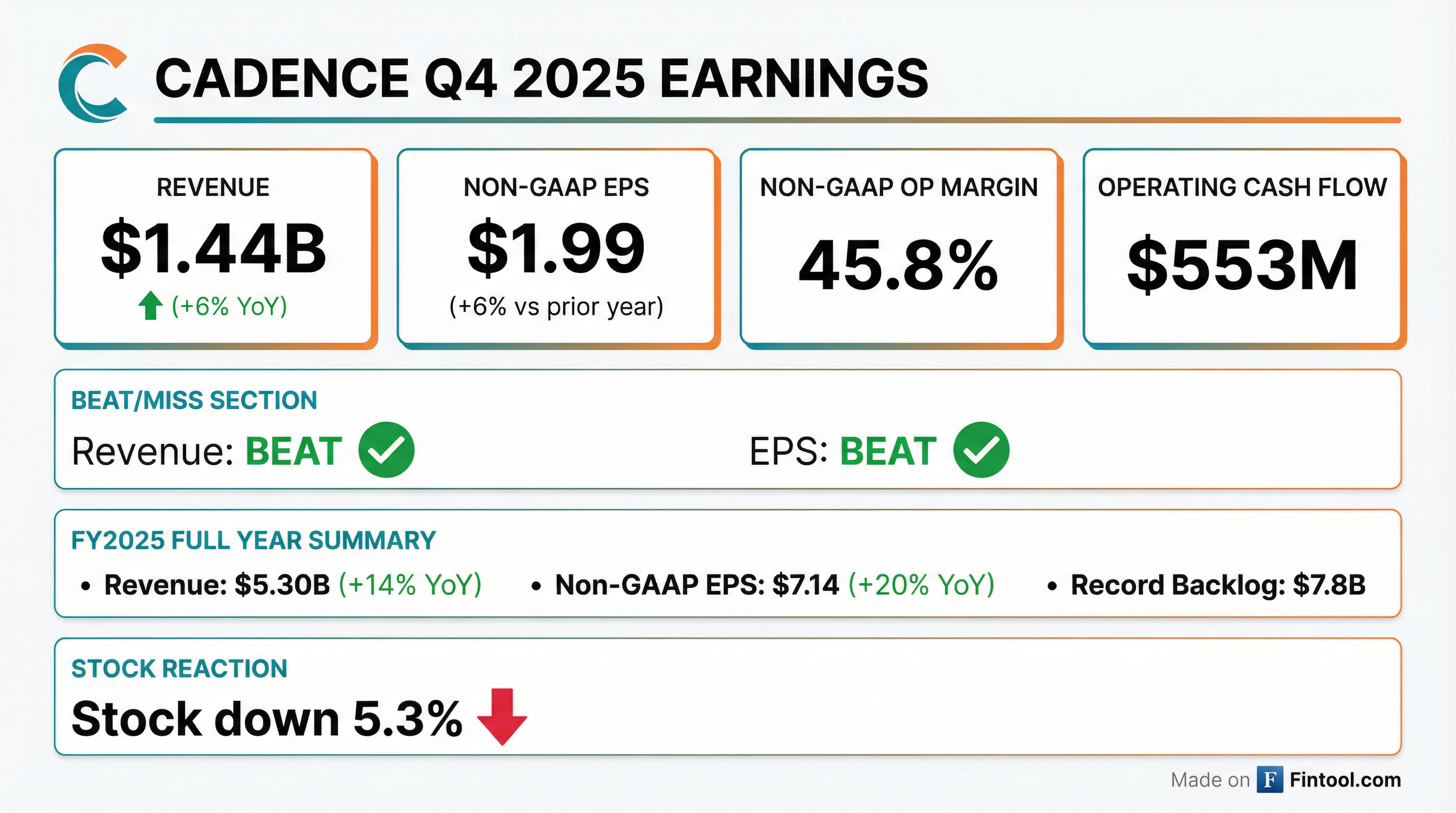

- Fiscal 2025 performance: revenue increased 14% to $5.297 billion, with a 44.6% non-GAAP operating margin, non-GAAP EPS of $7.14, and a record backlog of $7.8 billion

- Q4 2025 results: revenue of $1.44 billion, 45.8% non-GAAP operating margin, non-GAAP EPS of $1.99, operating cash flow of $553 million, ending cash of $3.001 billion versus $2.5 billion debt

- 2026 guidance: expects revenue of $5.9–6.0 billion, 44.75–45.75% non-GAAP operating margin, non-GAAP EPS of $8.05–8.15, $2 billion operating cash flow, and plans to repurchase ~50% of free cash flow

- AI-driven momentum: launched ChipStack AI Super Agent for automated chip design with up to 10× productivity improvement, expanded Cadence Cerebrus and AI agent workflows, and deepened partnerships with Broadcom, TSMC, Intel Foundry, and Samsung Foundry to deploy agentic AI solutions

- Cadence delivered total revenue of $1.44 billion in Q4 and $5.297 billion for FY 2025, up 14% year-over-year, exiting the year with a record backlog of $7.8 billion.

- FY non-GAAP EPS was $7.14 with non-GAAP operating margin of 44.6%, and Q4 non-GAAP EPS of $1.99.

- 2026 guidance targets revenue of $5.9 billion–$6.0 billion, non-GAAP EPS of $8.05–$8.15, and operating cash flow of approximately $2 billion.

- Launched AI-driven products including ChipStack AI Super Agent (up to 10× productivity improvement) and Tensilica HiFi iQ DSP (up to 8× AI performance gains).

- Returned $925 million to shareholders via buybacks in 2025, ending the year with $3.001 billion in cash and $2.5 billion of debt.

- Cadence posted Q4 revenue of $1.44 billion and full-year revenue of $5.297 billion (up 14% YoY), with a record backlog of $7.8 billion; Q4 GAAP/non-GAAP operating margins were 32.2%/45.8%, and non-GAAP EPS was $1.99 (FY 2025: $7.14).

- For 2026, the company guides revenue of $5.9 billion–$6.0 billion, non-GAAP EPS of $8.05–$8.15, and Q1 revenue of $1.42 billion–$1.46 billion with non-GAAP EPS of $1.89–$1.95.

- Continued AI momentum with the launch of ChipStack AI Super Agent (up to 10× productivity improvement) and scaled deployments of Cadence Cerebrus, Verisium, and Allegro X AI, backed by endorsements from Qualcomm, NVIDIA, Altera, and Tenstorrent.

- Core EDA revenue grew 13% in 2025; the hardware business had a record year with over 30 new customers; and IP revenue increased nearly 25% as AI, HPC, and automotive adoption expanded.

- Cadence posted Q4 2025 revenue of $1.440 billion (+6% YoY), with a GAAP operating margin of 32.2%, non-GAAP operating margin of 45.8%, GAAP EPS of $1.42, and non-GAAP EPS of $1.99.

- For FY 2025, revenue reached $5.297 billion (+14% YoY), non-GAAP operating margin was 44.6%, and non-GAAP EPS was $7.14.

- Year-end backlog hit a record $7.8 billion, with $3.8 billion expected to be recognized over the next 12 months from remaining performance obligations.

- Outlook for FY 2026: revenue of $5.9 billion–$6.0 billion, GAAP EPS of $4.95–$5.05, and non-GAAP EPS of $8.05–$8.15.

- Cadence introduced ChipStack, an AI-driven super agent for chip design and verification, built on its EDA platform to enhance productivity and convergence speed.

- Cadence delivered $1.440 billion in Q4 2025 revenue (vs. $1.356 billion in Q4 2024), with a 45.8% non-GAAP operating margin and $1.99 non-GAAP diluted EPS (vs. $1.88).

- For FY 2025, revenue grew 14% to $5.297 billion, non-GAAP diluted EPS increased ~20% to $7.14, and year-end backlog reached a record $7.8 billion.

- Outlook for FY 2026 includes revenue of $5.9 billion to $6.0 billion and non-GAAP diluted EPS of $8.05 to $8.15.

- Cadence announces the ChipStack AI Super Agent, the world’s first agentic AI workflow for automating front-end chip design and verification, delivering up to 10X productivity improvements in coding designs and testbenches.

- The solution orchestrates virtual engineers using Cadence’s foundational EDA tools, integrating optimization AI and supporting both cloud-based and on-premises frontier models like NVIDIA Nemotron and OpenAI GPT.

- Early deployments with Altera, NVIDIA, Qualcomm and Tenstorrent have begun; Altera reported a 10X reduction in verification effort, while Tenstorrent achieved up to 4X faster formal verification.

- ChipStack AI Super Agent is available now in early access, advancing Cadence’s Intelligent System Design strategy.

- Cadence has introduced ChipStack AI Super Agent, an “agentic” workflow to automate front-end chip design and verification, claiming up to 10x productivity improvements across coding, test planning, regression testing and debugging.

- The system integrates with Cadence platforms Verisium, Cerebrus and JedAI, and supports both cloud-hosted (OpenAI GPT) and on-premise frontier models (e.g., NVIDIA Nemotron).

- Early adopters include Nvidia, Qualcomm, Altera and Tenstorrent, as customers seek to address engineering shortages and accelerate AI-driven product cycles.

- Positioned under Cadence’s Intelligent System Design strategy, ChipStack builds a “mental model” of a chip’s intended function and leverages Cadence’s AI assistant tools, which have supported over 1,000 tapeouts to date.

- Cadence introduced the industry’s first LPDDR5X 9600 Mbps memory IP system solution for enterprise and data center AI/HPC applications, integrating production-proven LPDDR5X IP with Microsoft’s RAIDDR ECC algorithm for enhanced reliability.

- The solution delivers enterprise-grade RAS (reliability, availability and serviceability) with DDR5-style symbol-based ECC and sideband ECC support while maintaining a compact form factor and low power consumption.

- It supports 40-bit channels and offers sideband ECC performance comparable to DDR5 ECC implementations, targeting space-constrained, high-performance data center systems.

- Microsoft is the first customer to deploy this next-generation memory IP system, underscoring early industry adoption.

- Cadence reports $5.2–$5.3 billion in revenue, split roughly 70% EDA, 15% IP, and 15% systems, with a 14% revenue growth and 44.5% operating margin in the prior year.

- The company emphasizes a three-phase AI roadmap—infrastructure, physical/vertical, and science—and integrates AI into its design tools for 10%–20% PPA improvements.

- IP focus centers on HPC IP at advanced nodes (UCIe, HBM, DDR, PCIe, SerDes) plus Tensilica cores, targeting double-digit growth above company average.

- China business has rebounded to 11%–12% of revenue, exceeding earlier flat guidance, driven by infrastructure and physical AI chip designs.

- Hexagon acquisition aims to add multibody dynamics simulation for physical AI and 3D-IC workflows, supporting a > $1 billion systems run-rate post-integration.

- Cadence ended Q3 with a record backlog, achieved 14% year-to-date revenue growth, and anticipates another record backlog at Q4 close.

- Management outlined three AI phases—infrastructure (now–5 years), physical AI (3–7 years), and sciences AI (5–10 years)—and is applying AI to its EDA tools to target 10× productivity improvements.

- The Hexagon acquisition enhances Cadence’s systems segment by integrating multibody simulation for physical AI and complements its existing 3D IC offerings.

- Cadence sustains a 44–45% operating margin with organic incremental margins near 60%, allocates half of free cash flow to share buybacks, and maintains disciplined capital deployment despite selective M&A.

Quarterly earnings call transcripts for CADENCE DESIGN SYSTEMS.

Ask Fintool AI Agent

Get instant answers from SEC filings, earnings calls & more